Свободные инструменты для программирования FPGA

Подборка свободных инструментов для программирования FPGA, включающая в себя средства поддержки языков HDL, синтезаторы, симуляторы и некоторые другие.

Yosys

Yosys – проект по созданию свободного набора инструментов для программирования FPGA. В состав этих инструментов входят: yosys, nextpnr, icestorm, apicula, trellis. Подробнее ниже в соответствующих разделах обзора.

OSS CAD Suite

OSS CAD Suite – сборка свободно-распространяемых инструментов для разработки программ для FPGA. Собирается в рамках проекта Yosys. Доступны сборки для GNU/Linux, MacOS X и Windows. Включает в себя в частности: GHDL, Icarus Verilog, nextpnr, openFPGALoader, OpenOCD, Verilator, Yosys и множество других программ.

GHDL

GHDL – проект по разработке свободных инструментов для VHDL. Подробнее ниже в соответствующих разделах обзора.

Verilog и SystemVerilog

Yosys – синтезатор для Verilog.

Icarus Verilog – компилятор для Verilog.

Verilator – компилятор, симулятор и линтер для Verilog и SystemVerilog.

Verible – свободный набор инструментов для SystemVerilog от организации CHIPS Alliance. Включает в себя: линтер, форматер и сервер LSP.

SVLS – сервер LSP для языка SystemVerilog.

SVLint – линтер для языка SystemVerilog.

Veridian – сервер LSP для языка SystemVerilog.

VHDL

GHDL – компилятор, анализатор, симулятор и синтезатор для VHDL.

NVC – компилятор и симулятор для VHDL. Использует LLVM для компиляции в машинный код.

VHDL Language Server – сервер LSP для VHDL.

GHDL Yosys Plugin – дополнение к Yosys для поддержки VHDL с использованием GHDL.

Другие языки HDL

Chisel – HDL для описания цифровых схем уровня RTL. Chisel является DSL на базе языка программирования Scala.

SpinalHDL – HDL, являющийся DSL на базе языка Scala. Позиционируется как альтернатива для VHDL, Verilog и SystemVerilog.

Clash – язык HDL, имеющий синтаксис и семантику языка Haskell. Компилируется в VHDL, Verilog, SystemVerilog.

Veryl – HDL, написанный на Rust и заимствующий из него синтаксис и некоторые возможности. Позиционируется как альтернатива SystemVerilog.

SystemC – средства разработки на языке C++ для FPGA.

Intel Compiler for SystemC – компилятор компании Intel языка SystemC в SystemVerilog.

Place & Route

nextpnr

nextpnr – универсальная утилита, обеспечивающая этап Place & Route. Поддерживаются следующие чипы: Lattice iCE40, ECP5, Nexus; Gowin; Altera Cyclone V и некоторые другие. Является частью проекта Yosys.

Программаторы

openFPGALoader – универсальная утилита для записи прошивок в FPGA различных производителей, включая Anlogic, Cologne Chip, Efinix, Gowin, Intel (Altera), Lattice, Xilinx.

Проекты поддержки чипов

IceStorm – реверс-инжениринг, документация и примеры для чипов Lattice iCE40. Является частью проекта Yosys.

Apicula – проект, добавляющий к Yosys поддержку чипов компании Gowin семейств LittleBe и Arora.

Trellis – проект, добавляющий к Yosys поддержку чипов Lattice ECP5.

Oxide – проект по добавлению в Yosys поддержки для чипов Lattice Nexus.

Mistral – проект по добавлению к Yosys поддержки чипов Cyclone V.

Управление проектами

PYNQ – полный цикл разработки для чипов Xilinx на языке Python с использованием сервера Jupyter.

F4PGA – управление проектами с использованием только свободного ПО. Разрабатывается CHIPS Alliance.

PyFPGA – управление проектами разработки под FPGA, используя язык Python.

Разное

GTKWave – просмотрщик сигналов, записанных во время симуляции программ на Verilog и VHDL.

netlistsvg – программа построения диаграммы связей между электронными компонентами на основе файла netlist, сгенерированного Yosys.

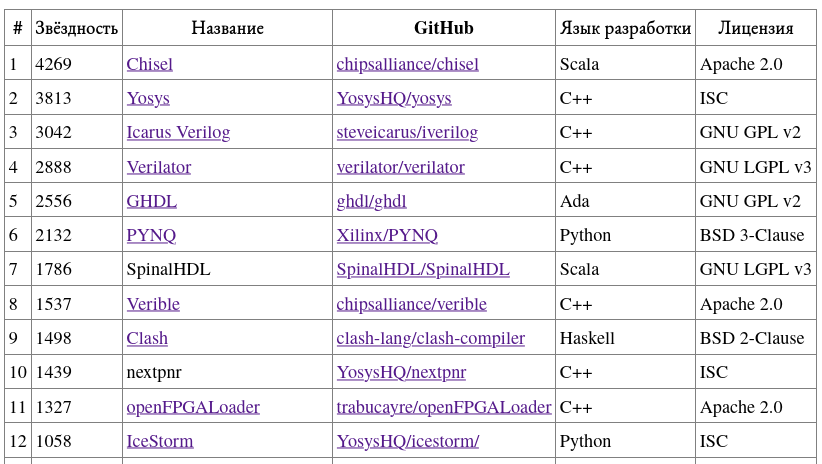

Сводная таблица свободных инструментов

Для удобства и оценки масштаба составил сводную таблицу, упорядочив по количеству звёзд на GitHub на момент написания статьи.

| # | Звёздность | Название | GitHub | Язык разработки | Лицензия |

|---|---|---|---|---|---|

| 1 | 4269 | Chisel | chipsalliance/chisel | Scala | Apache 2.0 |

| 2 | 3813 | Yosys | YosysHQ/yosys | C++ | ISC |

| 3 | 3042 | Icarus Verilog | steveicarus/iverilog | C++ | GNU GPL v2 |

| 4 | 2888 | Verilator | verilator/verilator | C++ | GNU LGPL v3 |

| 5 | 2556 | GHDL | ghdl/ghdl | Ada | GNU GPL v2 |

| 6 | 2132 | PYNQ | Xilinx/PYNQ | Python | BSD 3-Clause |

| 7 | 1786 | SpinalHDL | SpinalHDL/SpinalHDL | Scala | GNU LGPL v3 |

| 8 | 1537 | Verible | chipsalliance/verible | C++ | Apache 2.0 |

| 9 | 1498 | Clash | clash-lang/clash-compiler | Haskell | BSD 2-Clause |

| 10 | 1439 | nextpnr | YosysHQ/nextpnr | C++ | ISC |

| 11 | 1327 | openFPGALoader | trabucayre/openFPGALoader | C++ | Apache 2.0 |

| 12 | 1058 | IceStorm | YosysHQ/icestorm/ | Python | ISC |

| 13 | 1051 | OSS CAD Suite | YosysHQ/oss-cad-suite-build | – | ISC |

| 14 | 778 | GTKWave | gtkwave/gtkwave | C | GNU GPL v2 |

| 15 | 696 | netlistsvg | nturley/netlistsvg | JavaScript | MIT |

| 16 | 693 | NVC | nickg/nvc | C | GNU GPL v3 |

| 17 | 627 | Veryl | veryl-lang/veryl | Rust | Apache 2.0 |

| 18 | 552 | Apicula | YosysHQ/apicula | Python | MIT |

| 19 | 550 | SystemC | accellera-official/systemc | C++ | Apache 2.0 |

| 20 | 507 | SVLS | dalance/svls | Rust | MIT |

| 21 | 411 | Trellis | YosysHQ/prjtrellis | Python | Разные |

| 22 | 398 | VHDL Language Server | VHDL-LS/rust_hdl | Rust | MPL 2.0 |

| 23 | 387 | F4PGA | chipsalliance/f4pga | Python | Apache 2.0 |

| 24 | 345 | SVLint | dalance/svlint | Rust | MIT |

| 25 | 334 | GHDL Yosys Plugin | ghdl/ghdl-yosys-plugin | C++ | GNU GPL v3 |

| 26 | 272 | Intel Compiler for SystemC | intel/systemc-compiler | C++ | Apache 2.0 |

| 27 | 170 | Veridian | vivekmalneedi/veridian | Rust | MIT |

| 28 | 142 | Oxide | gatecat/prjoxide | Python | ISC |

| 29 | 133 | PyFPGA | PyFPGA/pyfpga | Python | GNU GPL v3 |

| 30 | 122 | Mistral | Ravenslofty/mistral | C++ | BSD 3-Clause |

Как мы видим, свободно-распространяемых инструментов набралось немало, а здесь перечислены не все. Эти инструменты покрывают возможно не все, но самые основные потребности разработчиков под FPGA, при этом нетребовательны к ресурсам, работают в различных операционных системах и постоянно развиваются. Но главное, они не привязаны к производителям чипов и могут использоваться с различными из них, хотя и не со всеми.

(c) Симоненко Евгений, 2025